## **Preface**

Espoo, November 25, 2019,

Hans Liljestrand

## **Contents**

| Pr        | eface   |          |                                         | 1  |

|-----------|---------|----------|-----------------------------------------|----|

| Co        | ntent   | S        |                                         | 3  |

| Lis       | st of F | Publicat | ions                                    | 5  |

| Au        | thor's  | s Contri | bution                                  | 7  |

| Ot        | her P   | ublicati | ons                                     | 9  |

| Lis       | st of F | igures   |                                         | 11 |

| Lis       | st of A | Abbrevia | ations                                  | 13 |

| 1.        | Intr    | oductio  | n                                       | 17 |

|           | 1.1     | Motiva   | u <mark>tion</mark>                     | 17 |

|           | 1.2     | Object   | ives                                    | 20 |

|           | 1.3     | Outlin   | e and contributions                     | 21 |

| 2.        | Bac     | kground  | l                                       | 23 |

|           | 2.1     | Compi    | lers                                    | 24 |

|           | 2.2     | Memor    | ry errors, attacks, and defenses        | 26 |

|           |         | 2.2.1    | From stack smashing to ROP              | 26 |

|           |         | 2.2.2    | Control-flow integrity                  | 29 |

|           | 2.3     | Memor    | ry safety                               | 30 |

|           |         | 2.3.1    | Spatial and temporal memory safety      | 31 |

|           |         | 2.3.2    | Temporal memory safety                  | 32 |

|           |         | 2.3.3    | Memory safety in C / C++                | 32 |

|           | 2.4     | Hardw    | are-assisted memory safety              | 33 |

| <b>3.</b> | Linu    |          | el memory safety                        | 35 |

|           | 3.1     | Backgr   | round: Intel MPX and reference counters | 36 |

|           |         | 3.1.1    | Reference counters                      | 36 |

|           |         | 3.1.2    | Intel MPX                               | 38 |

### Contents

|           | 3.2    | Results: refcount_t and MPX in the Linux kernel       | 40         |

|-----------|--------|-------------------------------------------------------|------------|

|           |        | 3.2.1 Preventing reference counter overflows in Linux | 40         |

|           |        | 3.2.2 Using Intel MPX in the Linux kernel             | 41         |

|           |        | 3.2.3 Discussion: tricky bugs and environments        | 41         |

| 4.        | Intel  | l SGX side-channels                                   | <b>45</b>  |

|           | 4.1    | Background: side-channels and Software Guard Exten-   |            |

|           |        | sions (SGX)                                           | 46         |

|           | 4.2    | Results: preventing SGX branch shadowing              | 49         |

|           | 4.3    | Discussion: side-channel challenges                   | 49         |

| <b>5.</b> | ARM    | I Pointer authentication                              | <b>5</b> 3 |

|           | 5.1    | Background: ARMv8.3-A pointer authentication          | 53         |

|           | 5.2    | Results: pointer authentication and stack safety      | 55         |

|           | 5.3    | Discussion: beyond pointer authentication             | 57         |

| <b>6.</b> | Disc   | ussion and Conclusion                                 | 61         |

|           | 6.1    | Preventing memory errors in unsafe languages          | 61         |

|           | 6.2    | Memory safe languages                                 | 62         |

|           | 6.3    | Understanding memory errors and exploitability        | 64         |

|           | 6.4    | Conclusion                                            | 65         |

| Er        | rata   |                                                       | 83         |

| Pu        | blicat | ions                                                  | 85         |

### **List of Publications**

This thesis consists of an overview and of the following publications which are referred to in the text by their Roman numerals.

- I Elena Reshetova, Hans Liljestrand, Andrew Paverd, N. Asokan. Towards Linux Kernel Memory Safety. *Software: Practice and Experience*, December 2018.

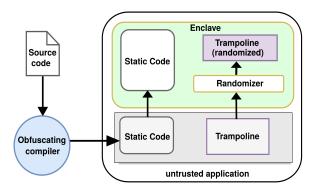

- II Shohreh Hosseinzadeh, Hans Liljestrand, Ville Leppänen, Andrew Paverd. Mitigating Branch-Shadowing Attacks on Intel SGX using Control Flow Randomization. In *Proceedings of the 3rd Workshop on System Software for Trusted Execution, SysTEX '18*, Toronto, ON, Canada, pages 22–47, October 2018.

- III Hans Liljestrand, Thomas Nyman, Andrew Paverd. PAC it up: Towards Pointer Integrity using ARM Pointer Authentication. In Proceedings of the 28th USENIX Security Symposium, Santa Clara, CA, USA, pages 177–195, August 2019.

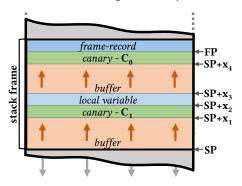

- IV Hans Liljestrand, Zaheer Gauhar, Thomas Nuyman, Jan-Erik Ekberg, N. Asokan. Protecting the stack with PACed canaries. In Proceedings of the 4th Workshop on System Software for Trusted Execution, SysTEX '19, Huntsville, ON, Canada, 6 pages, October 2019.

- V Hans Liljestrand, Thomas Nyman, Lachlan Gunn, Jan-Erik Ekberg, N. Asokan. PACStack: an Authenticated Call Stack. Submitted, 21 pages, August 2019.

### **Author's Contribution**

### Publication I: "Towards Linux Kernel Memory Safety"

I designed and implemented a GCC-plugin that enabled the use of Intel MPX within the Linux kernel. I also contributed to the design of a hardened reference counter for the Linux kernel. Together with my co-authors, I implemented over 200 patches that were subsequently accepted in the mainline Linux kernel. I wrote the paper together with my co-authors.

# Publication II: "Mitigating Branch-Shadowing Attacks on Intel SGX using Control Flow Randomization"

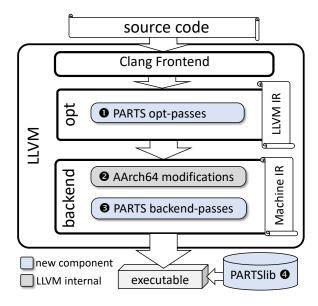

I co-designed a control-flow randomization scheme that mitigates branch-shadowing side-channels on Intel SGX enclaves. I implemented the LLVM-based compile-time instrumentation together with my co-authors. I wrote the paper together with my co-authors.

## Publication III: "PAC it up: Towards Pointer Integrity using ARM Pointer Authentication"

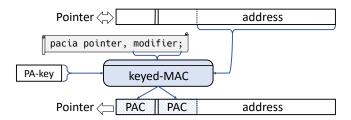

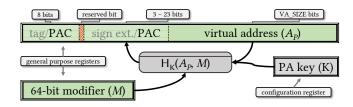

I co-designed a run-time type-safety scheme based on ARMv8.3-A Pointer Authentication (PA). Together with my co-authors, I investigated and proposed a mitigation to a PA-specific pointer reuse attack. Thomas Nyman and I led the writing of the paper, to which all authors contributed.

### Publication IV: "Protecting the stack with PACed canaries"

I co-designed a stack-canary scheme built upon ARMv8.3-A Pointer Authen-

tication and led the implementation of an LLVM-based research prototype. I led the writing of the paper, to which all authors contributed.

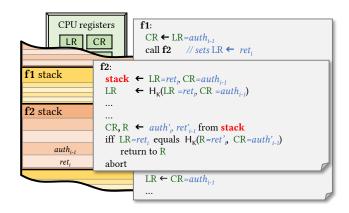

### Publication V: "PACStack: an Authenticated Call Stack"

I co-designed a ARMv8.3-A Pointer Authentication scheme that provides precise return address protection. Thomas Nyman envisioned the initial design, whereas I proposed PA-specific optimizations. I implemented the LLVM-based prototype of the design. Thomas Nyman and I led the writing of the paper, to which all authors contributed.

## **Other Publications**

The following publications are not included in this dissertation.

- VI Mika Juuti, Christian Vaas, Ivo Sluganovic, Hans Liljestrand, N. Asokan, Ivan Martinovic. STASH: Securing transparent authentication schemes using prover-side proximity verification. *Proceedings of the IEEE International Conference on Sensing, Communication and Networking*, 2017.

- VII Hans Liljestrand, Thomas Nyman, Jan-Erik Ekberg, N. Asokan. Late Breaking Results: Authenticated Call Stack. *Proceedings of the 56th Annual Design Automation Conference*, 2019.

- VIII Long Cheng, Hans Liljestrand, Md Salman Ahmed, Thomas Nyman, Danfeng (Daphne) Yao, Trent Jaeger, N. Asokan. Exploitation techniques and defenses for data-oriented attacks. *Proceedings of the IEEE Cybersecurity Development*, 2019.

# **List of Figures**

| 2.1 | Program abstraction layers                      | 24 |

|-----|-------------------------------------------------|----|

| 2.2 | Three-part compiler construction                | 25 |

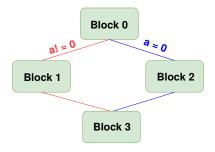

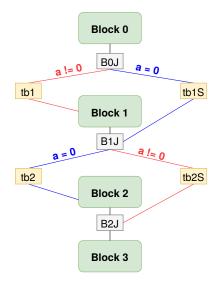

| 2.3 | Temporal and spatial memory errors              | 31 |

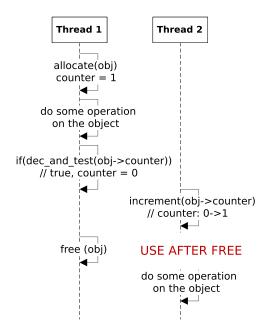

| 3.1 | Reference counters and concurrency.             | 38 |

| 3.2 | Intel MPX metadata addressing scheme.           | 39 |

| 4.1 | Intel SGX overview                              | 46 |

| 4.2 | Branch-shadowing side-channel                   | 48 |

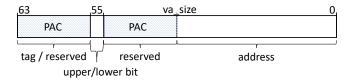

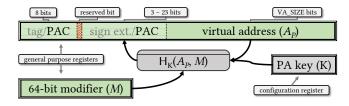

| 5.1 | Pointer authentication codes in pointers on ARM | 54 |

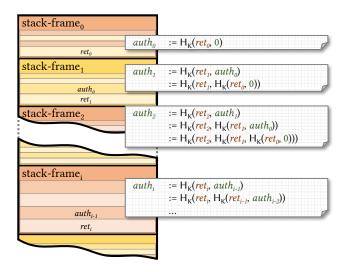

| 5.2 | Validating returned addresses with a MAC chain  | 56 |

## **List of Abbreviations**

ABI application binary interface

**API** application programming interface

ASLR address space layout randomization

**BD** bound directory

BPU branch prediction unit

BT bound table

BTB branch target buffer

BTI branch target indicator

**CCFI** cryptographic CFI

**CET** Control-flow Enforcement Technology

CFG control-flow graph

**CFI** control-flow integrity

CISC complex instruction set computer

**CPU** central processing unit

**DEP** data-execution prevention

**DOP** data-oriented programming

**DOS** denial-of-Service

EC equivalence class

FP frame pointer

FSM finite state machine

**IBRS** indirect branch restricted speculation

**IoT** Internet of Things

IR intermediate representation

**JIT-ROP** just-in-time return-oriented programming

**JOP** jump-oriented programming

KASLR kernel address space layout randomization

LBR last branch record

LR link register

MAC message authentication code

MMU memory management unit

**MPX** Memory Protection Extensions

MTE Memory Tagging Extension

**OS** operating system

**PA** Pointer Authentication

PAC pointer authentication code

**PHT** pattern history table

PKU Memory Protection Keys for Userspace

PT Processor Trace

RISC reduced instruction set computer

**ROP** return-oriented programming

**SGX** Software Guard Extensions

**SP** stack pointer

**SROP** sigreturn-oriented programming

**SSA** single static assignment

**TEE** trusted execution environment

**TOCTOU** time-of-check-time-of-use

VA virtual address

VM virtual machine

#### **Abstract**

Computers today are ubiquitous and closely integrated into our every-day lives. But computers are fickle in nature. Programs are written by fallible humans and run on imperfect hardware. As a result, computer systems are plagued by memory vulnerabilities. Many remedies exist; from defensive programming techniques to memory-safe languages. But these approaches require security-expertise and costly porting of existing code. To achieve wide-spread use, we must integrate security into existing tools and languages. Moreover, this must be done with minimal performance and deployment costs. New security features are being rolled out in commodity hardware. They hold the promise of security, but are non-trivial to use effectively. In this dissertation, I show how compile-time instrumentation can use such hardware for performant memory-safety solutions.

We explore the recently introduced ARMv8.3-A Pointer Authentication (PA) and Intel Memory Protection Extensions (MPX) extensions. PA supports hardware-accelerated signing and verification of pointers. Not only do we address weaknesses in prior PA-based defenses, but we also present novel solutions for memory safety. In particular, we demonstrate how PA can be used for run-time type checking, precise return address protection, and stack safety. Userspace MPX-instrumentation is well-known and uses in-memory metadata to provide bounds checking of memory accesses. The kernel is paramount for security, but using MPX to protect is not straightforward. Because the kernel must manage its own memory, the MPX metadata is not feasible to use. We show how to avoid this issue using kernel-specific MPX instrumentation. But security hardware—such as the Intel Software Guard Extensions (SGX)—can itself be vulnerable. We investigate Intel SGX side-channels, and show how compile-time instrumentation can be used to mitigate a branch-shadowing attack on SGX.

This dissertation presents security schemes that achieve minimal performance overheads by using features in off-the-shelf hardware. Our compile-time instrumentation integrates these features into existing code, without developer intervention. Together, hardware-assistance and compile-time instrumentation paves the way towards security solutions that offer optimal trade-offs in terms of development, deployment and performance costs. Yet, there are many roads ahead. Future work should explore compatibility with real code-bases, for instance, when common programming patterns rely on undefined behavior. Support should also be extended to C++ and other languages; this requires support for new language constructs such as exceptions and polymorphic types. Memory-safe languages could also benefit from hardware-assisted security, for instance, by providing fault isolation or improving performance of existing checks. Together, these directions will allow deployable security along a broad spectrum of projects

List of Abbreviations

and developers.

### 1. Introduction

### 1.1 Motivation

Computer systems are everywhere today. This has been a growing trend for decades, from personal computing and mobile phones to the Internet of Things (IoT). The transition has not been easy from a security perspective. Personal computing moved computers from physically secured server rooms into open environments. With the emergence of the Internet, computers were further opened to network attacks. In time, operating systems were forced to adapt and improve their built-in security. A similar progression happened with web technologies, which, after some initial security-woes, have become gradually more secure.

Computers have also become more integrated into our everyday lives. Even devices without obvious privacy or security concerns (e.g., toys or other gadgets) can be abused. The Mirai attacks in 2018 compromised IoT devices to mount a massive denial-of-Service (DOS) attack that crippled large parts of the Internet [7]. Security is no longer the concern of a few security-critical systems. It spans everything from smart refrigerators and gaming consoles to cyber-physical systems such as autonomous vehicles.

The widespread use of computers is not limited to the consumers; computer systems need to be designed and implemented. Easy access to software development tools and distribution channels has enabled development outside large organizations. With the recent growth of maker workshops and open hardware designs (e.g., RISC-V [12]), the same trend increasingly applies to hardware development as well. These new systems must be secured, but often the designers of these systems are not security experts. Vulnerabilities that arise from application-specific requirements and logic errors can, or must, be addressed by the developer. *Memory errors* are a prominent cause of many security problems. They are often unintuitive and difficult for non-experts.

**Memory errors** *Memory errors* are faults that cause memory to be altered in unintended ways [151]. The underlying issue can be in the architecture-specific details of language implementations (e.g., how function calls are implemented). Because they depend on low-level details, they are not necessarily apparent from source code alone. As such, a higher level of security expertise and awareness is required to mitigate these attacks. The same applies to *software side-channels*, e.g., prime+probe attacks that exploit the central processing unit (CPU) caches [167]. Not to mention the recent *transient execution attacks* that leverage obscure micro-architectural behavior [27].

An attacker can exploit memory errors to alter program behavior or expose sensitive data. The *stack smashing* attack from 1996 [108]—and the Morris worm from 1988 [149]—exploits memory errors to inject code on the stack and then alters the function return address so that the injected code is executed on return. This attack type is prevented by widely-deployed W PX policies such as the data-execution prevention (DEP) feature on Microsoft Windows [116]. Yet the 1997 *return-to-libc* attack showed that expressive attacks are possible to construct without injecting new code into program memory [130]. These attacks are mitigated by stack canaries [47], address space layout randomization (ASLR) [142], and control-flow integrity (CFI) [2], which in turn can be defeated by newer attacks, and so on.

The continuous arms race and increasingly obscure attacks require constant evolution of security mechanisms [151]. Because security today touches all areas of software development, it cannot depend on security experts or *ad hoc* solutions. Instead, security must be supported from the ground up, starting with the tools used to build software. Secure programming languages—such as the systems programming language Rust [114]—show promise in preventing memory errors. But new languages cannot replace the expertise and code that already exist in older languages. To protect code today, we must accommodate programming languages in current use.

**Memory protection** Much research has focused on providing memory safety for memory-unsafe languages, such as C/C++. Such approaches can be categorized into *compile-time* and *binary-only* instrumentation. Binary-only approaches can be applied to compiled binaries and are convenient to use, but cannot rely on language semantics available at compile-time. Compile-time instrumentation can use language semantics such as variable scoping and type information to implement more precise security policies. Compile-time approaches can be further divided into three categories: 1) new memory-safe languages, 2) augmenting memory-unsafe languages, and 3) source-compatible hardening of existing languages.

Although memory-safe languages cannot immediately replace existing code, they are an important step towards memory safety. They are powerful because security properties, such as variable ownership and array bounds, can be made first-class language constructs [114]. The same can be achieved by augmenting memory-unsafe languages such as C with new annotations and types that provide memory safety [60]. Although such hardened C variants can be applied to existing codebases, they require refactoring and code conversion, which can incur a considerable deployment cost. Finally, security mechanisms can be added to the compilation of an existing language. These approaches rely on existing semantic information and static analysis to implement security features without requiring source code changes.

Hardware-assisted memory protection From an instrumentation standpoint, hardening mechanisms can be purely software-based [113, 121], or rely on special-purpose hardware. Software-based solutions are convenient, but typically suffer from high performance overheads or security trade-offs (e.g., CCFI with an overhead of 50% [113], or software shadowstacks that are vulnerable to memory disclosure [25]). Several hardwarebased approaches have been proposed in the research literature (e.g., CHERI [162], HardBound [54], and HardScope [123]), but these require special-purpose hardware. Meanwhile, new security extensions are being deployed in commodity hardware (e.g., Intel Memory Protection Extensions (MPX) [125], Intel Control-flow Enforcement Technology (CET) [82], ARM8.3-A Pointer Authentication (PA) [133], ARM8.5-A Memory Tagging Extension (MTE) [9]). These features are as of yet not used to their fullest extent, or in the case of special-purpose hardware, are costly to deploy. Nonetheless, hardware-assisted memory safety provides fertile ground for building efficient security mechanisms. Features in commodity hardware are particularly interesting as they allow wide-scale deployment with no additional hardware costs.

Kernel hardening The operating system (OS) kernel controls the whole system and is an enticing attack target. By exploiting the kernel, an attacker can gain full access to a system, e.g., by controlling process scheduling and memory mapping. The security of the kernel is thus critical for the whole system's security. The Linux kernel is widely deployed on a range of devices, including IoT and other embedded devices. In contrast to desktop systems, it might not be possible to update embedded devices after deployment. A reactive patching strategy is thus ineffective. Kernel development must instead provide systematic approaches that eliminate whole classes of errors. Meanwhile, many memory safety efforts focus on userspace programs and cannot be directly transferred into the kernel. Intel MPX, for instance, provides configuration registers for kernel space but uses a metadata model that cannot be used within the Linux kernel [125]. But the constrained low-level environment is not always a hindrance. The homogeneous source code of the kernel can allow solutions

that are not applicable to general code, e.g., by modifying definitions in common headers and subsystems.

### 1.2 Objectives

The overarching objective of this work is to harden computer systems against run-time attacks that exploit memory errors or side-channels. But security hardening cannot be our only goal; solutions must also be deployable, both in terms of development cost and performance. In practice, our objective is thus to leverage existing hardware and provide source-compatible security schemes with a low-barrier of adoption. However, protecting a regular userspace application running on a compromised kernel is futile. As a consequence, the security of the OS kernel must be considered.

**Compile-time instrumentation** For a large class of programs, deployment costs exclude developer-intensive approaches such as switching to new or hardened languages. Compile-time instrumentation provides a solution as it uses existing source-code semantics to instrument programs with run-time checks. But instrumentation will change program behavior; and can lead to compatibility issues (e.g., when a program relies on specific undefined behavior in C / C++). In this dissertation, as a whole, I explore the research question:

# RQ1 How to improve memory safety using compile-time instrumentation?

Hardware-assistance Many security mechanisms incur a large performance overhead and therefore necessitate trading off security to keep overhead within acceptable bounds. Hardware support allows for both better performance and security. But new hardware is expensive. One objective of this work is to explore the use of existing and upcoming hardware security extensions in commodity hardware. In general, I aim to answer the following research question:

# RQ2 How can security features in commodity hardware be used to harden memory safety?

**Kernel hardening** Due to its central role, the kernel must be protected to prevent full system compromise. This work specifically targets systematic approaches that eliminate classes of memory errors, not individual bugs. Existing memory-safety research often focuses on userspace applications.

Table 1.1. Publications and corresponding research questions.

| Publication     |             | RQ1 | RQ2 | RQ3 |

|-----------------|-------------|-----|-----|-----|

| Publication I   | (Chapter 3) | ✓   | ✓   | ✓   |

| Publication II  | (Chapter 4) | ✓   | X   | X   |

| Publication III | (Chapter 5) | ✓   | ✓   | X   |

| Publication IV  | (Chapter 5) | ✓   | ✓   | X   |

| Publication $V$ | (Chapter 5) | ✓   | ✓   | X   |

These solutions either cannot be realized in kernel space, or they require additional changes to function properly. One objective is thus exploring the adaptation of such technologies to protect the kernel. The self-contained nature of the kernel can also lend itself to more hands-on approaches that modify the kernel source itself. However, it is not straightforward to develop and apply kernel-wide patches in a systematic way. Through this work, I explore these problems, and in particular, aim to answer the following research question:

RQ3 How can the OS kernel's memory safety be hardened in a systematic way?

### 1.3 Outline and contributions

This thesis is organized such that Chapter 2 offers a common background upon which subsequent chapters build. The following three chapters (Chapters 3–5) summarize the work in the five publications that comprise this dissertation. The relation between the publications and the research questions are summarized in Table 1.1. Two central themes emerge in this dissertation: compile-time instrumentation and hardware-assisted security.

Chapter 3 presents Publication I, which explores research question RQ1. Specifically, we address two categories of memory errors in the Linux kernel. First, we apply a kernel-wide protection scheme against reference counter overflows. We also propose an automated source code checking tool that encourages the secure implementation of new reference counters. Patches for both reference counter protection and code checking were subsequently accepted in the upstream Linux kernel [43]. Second, we also touch RQ2 and RQ1, by adapting the Intel MPX instrumentation for in-kernel protection.

Chapter 4 presents Publication II, in which we address a side-channel vul-

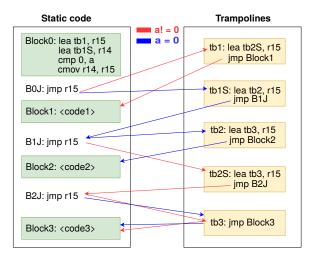

nerability in Intel Software Guard Extensions (SGX). SGX is a userspace trusted execution environment (TEE) that provides isolated execution and encrypted memory within an *enclave*. The enclave provides both integrity and confidentiality guarantees, even against the OS. Unfortunately, SGX is vulnerable to side-channel attacks. Publication II addresses **RQ1** by employing compile-time instrumentation to prevent a branch-shadowing side-channel on Intel SGX.

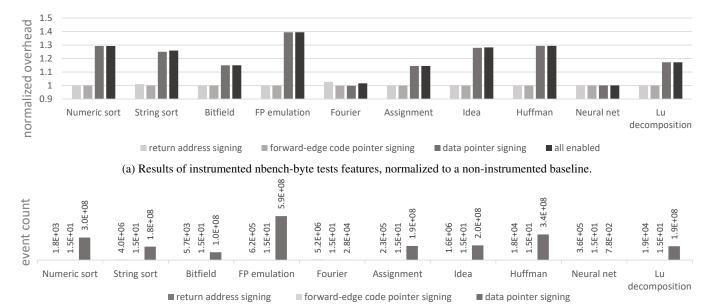

Chapter 5 presents Publications III—IV, which all explore the ARMv8.3-A PA [8] hardware extension (RQ2). In Publication III we show how to mitigate a PA-specific reuse attack and implement PA-based run-time type enforcement for C. In Publication IV we show how PA can be used to harden traditional stack canaries, whereas Publication IV shows that we can eliminate the reuse attack completely for specific attacks. These works answer RQ2 and RQ1 by showing that compile-time instrumentation using commodity hardware can provide security with negligible performance overheads.

## 2. Background

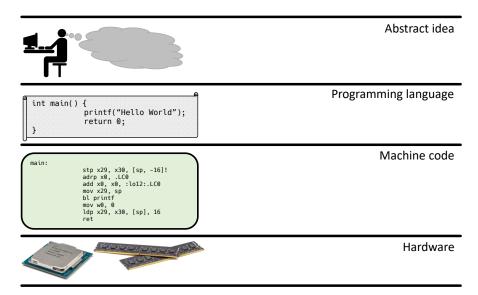

Computer programs can be viewed through different layers of abstraction (Figure 2.1). A programmer does not interact directly with the hardware. Instead, they use a high-level programming language—e.g., C, C++, Java, Python—to describe intended functionality in source code. A compiler then translates the source code into *machine code* for a specific machine. Finally, the machine code is loaded into a physical machine that executes it. The programmer focuses on the source code, but the machine code directly affects run-time performance. Consequently, programmers often employ various techniques—e.g., inline assembly and code patterns with predictable compiler output—to produce machine code that is optimal for specific hardware. But consequences are not limited to performance; memory errors and side-channels are a direct consequence of how highlevel logic is realized on specific hardware.

As an example, consider a local variable in the C language. It must be assigned a specific memory area whose size is determined based on the variable size. At run-time, the machine code does not account for variable sizes, and so might cause an overwrite memory error. Data is often stored in contiguous memory areas to improve performance. An overwrite will thus likely corrupt memory belonging to another variable, and thus be exploitable. The CPU caches memory accesses to improve performance. However, because the CPU caches are not tied to the process, they can be used as a side-channel to infer memory accesses of other processes executing on the same CPU [167].

The works included in this dissertation all use compile-time instrumentation. It is useful to consider how a compiler works in order to appreciate its relation to memory safety. Section 2.1 presents compiler internals. Section 2.2 discusses memory error exploitation techniques and defenses. Section 2.3 looks at memory safety. Finally, in chapter Section 2.4, I discuss hardware-assisted memory-safety defenses.

<sup>&</sup>lt;sup>1</sup>I will not consider interpreted languages or just-in-time compilation, although most of the discussion in this dissertation also applies to them.

**Figure 2.1.** A computer program can be viewed from three different layers: the source programming language, the machine code that is given to the CPU, and the hardware that executes the computations described by the machine code.

### 2.1 Compilers

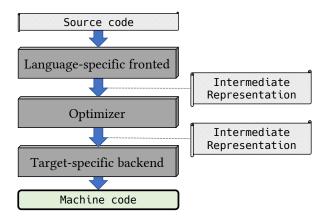

A compiler typically consists of three main components (Figure 2.2): 1) a frontend that understands, parses and transforms some input language into an intermediate representation (IR), 2) an optimizer that transforms the IR to improve it without impacting the end results, and 3) a backend that transforms the IR into some destination language, typically the machine code of a targeted processor architecture. These descriptions are intentionally imprecise; for example, "improving" might mean reducing size or execution time, or minimizing memory use. The distinction between these components is also loose; in practice, they can be more or less integrated. Nonetheless, this is a useful view of the compilation process and describes the general architecture of, for instance, the LLVM / Clang compiler [106].

**Frontend** The compiler frontend recognizes a source languages and transforms them into an IR used by the compiler. The frontend understands the *syntax* and *semantics* of the source language. It can thus validate the structure, and to some extent, the meaning of the program. The front-end can also perform extensive analysis by leveraging source code semantics. For instance, the Clang compiler provides various static analyzers that can be used to detect memory errors at compile time [36]. Other languages, such as Rust, perform static analysis during compilation in order to provide strong run-time security properties [114].

After validating the input, the frontend converts it to a common IR used by the compiler. In compilers such as LLVM, the IR is shared by multiple frontends for different languages. Although the IR is typically language

**Figure 2.2.** A compiler performs three main functions: 1) it recognizes an input language, 2) it optimizes the code, and 3) it outputs the result in come output format.

agnostic, different frontends will produce slightly different IR. The target architecture might also impose limitations that affect the produced IR. The C language, for instance, defines integer sizes that are dependent on the target architecture. Consequently, a C language frontend outputs slightly different IR on 32-bit and 64-bit architectures.

**Optimizer** The optimizer performs various analyses and uses the results to improve the IR. Most optimizations are performance-related. An example would be a loop optimization that moves a constant assignment out of the loop so that it is only executed once. The IR is designed to facilitate efficient optimizations and code generation. In LLVM, the IR is in single static assignment (SSA) form, i.e., each variable is assigned only once. The SSA simplifies reasoning about variable values and lifetimes.

The IR operates on an abstract machine model that has an unlimited number of registers to hold variables. Nonetheless, it does incorporate memory store and load operations, for instance, to load global variables. Optimizations then try to minimize the need for memory operations to improve performance. For instance, when a loop loads a variable from memory, it would be beneficial to move the load outside the loop. But the optimizer must not change the functionality of the program. Hence, it must first prove that the loaded memory cannot change during the loop. This might require *points-to analysis* that shows which pointers could point to the same memory at run-time [6, 150].

**Backend** The compiler backend converts the hardware-agnostic IR into machine-specific code. In the case of LLVM, this is another IR, called simply the machine IR. The machine IR syntax is shared among different architectures, which then use it to describe architecture-specific instructions. The conversion of SSA form IR must perform two critical functions: 1) instruction selection, which selects target-specific instructions that correspond to some IR instruction, and 2) register selection, which assigns each IR variable to a specific hardware register. Because the hardware registers

are limited in number, the compiler must sometimes *spill* variables into memory. Specifically, onto the function stack.

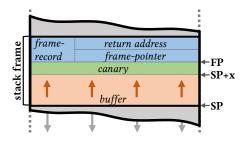

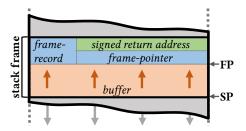

The stack size must be defined, for which the compiler must decide which values it needs to hold. The calling convention will typically set some constraints on the stack layout. Function parameters might be passed through the stack, for instance. The stack frame also typically holds control-data needed to implement function calls, namely: 1) the frame pointer (FP) that indicates the address of the previous stack frame, and 2) the return address, which indicates where execution should continue after the current function.

It is at this final stage, after various transformations, where memory errors materialize. Neither the IR nor machine IR know the semantics of the original input language. As such, either the original code or the various transformations after it could be based on incorrect assumptions. When these are not explicitly checked, either via compile-time verification or run-time checks, memory errors occur. Moreover, hardware limitations mean that control-data such as the return address is stored interleaved with other data on the stack. This allows seemingly small memory errors to affect program operation drastically.

### 2.2 Memory errors, attacks, and defenses

It is useful to review the history of memory attacks and defenses in order to appreciate the current state of run-time memory protection. In this section, I will present the early progression of attacks, from code injection [149, 108] to return-oriented programming (ROP) [141]. Along the way, I will present the evolution of related defenses and their subsequent circumvention techniques. I will finally present current research and directions in memory protection.

### 2.2.1 From stack smashing to ROP

**Code injection attacks** Buffers allocated on the stack have a specific size at run-time. A stack-based buffer overflow happens when a write to such a buffer exceeds that size and corrupts other memory. An overflow could happen because the size of input provided by an attacker  $\mathscr A$  is not verified to be within expected size limits. The traditional *stack smashing* attack exploits such overflows to inject attacker-controlled machine code onto the stack [149, 108]. To execute the code,  $\mathscr A$  alters the program control flow by exploiting the implementation of functions.

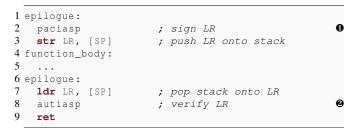

On complex instruction set computer (CISC) architectures such as x86, a function call implicitly stores the return address on the stack before transferring control into the function. Correspondingly, the return instruc-

tion then implicitly loads the return address from the stack and transfers control to the pointed-to address. On reduced instruction set computer (RISC) architectures, e.g., ARM, the return address is stored in the link register (LR) on function entry [10]. Nonetheless, it must then be stored on the stack to facilitate nested function calls that overwrite LR. In both cases, the return address is thus stored on the stack.  $\mathscr A$  can thus not only inject the machine code but also corrupt the return address such that it points to the injected code.

$W \oplus X$  policies  $W \oplus X$  policies enforce that memory is either writeable or executable but not both at the same time. They effectively prevent code injection attacks by making the stack non-executable. A non-executable stack does not stop memory errors from corrupting memory. Instead, it prevents  $\mathscr A$  from executing the injected code. Today,  $W \oplus X$  policies are widely supported by operating systems, including Microsoft DEP [116] and Linux [129].

**return-into-libc** The 1997 return-into-libc attack demonstrated that injected code is not necessarily needed [130]. In this attack,  $\mathscr A$  replaces the function return address with the address of a libc function. The victim will then incorrectly return to the injected address and execute the attacker-chosen libc function. This technique allows  $\mathscr A$  to effectively call arbitrary functions. Moreover, because the stack grows towards lower addresses,  $\mathscr A$  can corrupt multiple stack-frames.  $\mathscr A$  can thus inject several return addresses such that the program executes multiple functions of the attackers choosing.

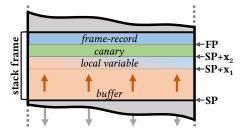

**Stack canaries** Although the return-into-libc attack is sophisticated, it still exploits a stack buffer overflow. As such, it can be prevented by detecting overflows before the function return is executed. Stack canaries, proposed initially in StackGuard [47], build upon this realization. A stack canary is a value that is stored on the stack such that it will be corrupted if an overwrite reaches the return address. The integrity of the canary can then be verified before the function returns.

A can circumvent canary defenses by guessing the correct canary value, or by corrupting non-protected data on the stack [1, 135]. Overflows that exploit string functions can be prevented using *terminator canaries* that include string-terminating characters [46]. Early defenses prevented canary copy and re-use attacks by masking the canary with the return address [61]. Several hardened canary schemes exist, including DynaGuard [131] and DCR [76] that allow re-randomizing canary values at run-time; and polymorphic canaries [160] that allow efficient diversification of canaries in forked processes.

In practice, canary schemes are very similar to the original StackGuard. Both GCC and Clang provide stack protection using canaries [70, 35]. The instrumentation initializes a single process-wide canary at startup.

The compilers offer different variants of the stack protector, but these only control which functions are instrumented. For instance, a canary in a function without buffers is unlikely to be useful, and so it can be omitted. Ultimately, any canary scheme can be circumvented by avoiding overwriting the canary or by leaking its value. This inherent weakness makes the performance cost of hardened canary schemes questionable.

Code-reuse attacks  $W \oplus X$  policies or canaries can not prevent all returninto-libc attacks, or, more generally, code-reuse attacks. ROP is an advanced code-reuse technique that can be used to realize expressive attacks [141]. In ROP,  $\mathscr A$  changes multiple return addressees on the stack such that they point into gadgets. In contrast to return-into-libc, a gadget is not necessarily a complete function. Instead, it can be any section of code that ends in a return. The return is used to chain gadgets together.  $\mathscr A$  can use ROP for arbitrary computation by finding and using different gadgets, e.g., memory load and store gadgets.

Subsequent research has demonstrated that ROP attacks are possible on ARM architectures [97, 49]. Others have demonstrated that jump-oriented programming (JOP) attacks can achieve similar expressibility without return instructions [31, 18]. Instead, JOP attacks use sequences of instructions with similar behavior. For instance, instead of a return, a JOP gadget could end with an indirect branch instruction. Other attacks exploit the behavior of abnormal control-flow transitions, such as signal handlers. When entering a signal handler, the execution state is stored in a *signal frame* on the program stack. On return from the handler, the signeturn system call restores the prior execution from the signal-frame and resumes execution. Signeturn-oriented programming (SROP) attacks exploit this behavior by writing a bogus signal-frame on the stack and performing a signeturn system call [19].

**Probabilistic defenses** Code-reuse attacks depend on finding gadgets. A typical program contains a large amount of code, and so gadgets are typically available. A can thus analyze a target binary, identify the gadgets, and store their memory addresses. Address space layout randomization (ASLR) randomizes the location of different memory regions to remove predictable gadget addresses [128, 163]. To perform a code-reuse attack, A must either leak addresses or attempt to guess them, which likely causes the program to misbehave or crash. ASLR can also be applied to protect the OS kernel [92]. Both Windows [87] and Linux [42] now make use of ASLR to protect both the kernel and userspace applications.

Side-channel attacks can break ASLR in both userspace [73, 62] and in the kernel [80]. The kernel is at a disadvantage because it is long-lived and interacts with multiple different programs. Any program, log, or driver could be used to leak kernel addresses for an attack launched from another process. It is likely also non-trivial to transfer ASLR hard-

ening schemes, such as re-randomization [112, 161], to a kernel setting. Moreover, advanced attack techniques such as just-in-time return-oriented programming (JIT-ROP) can discover new gadgets while executing a ROP attack [145]. JIT-ROP works around fine-grained ASLR schemes, but would likely apply equally to re-randomization schemes.

### 2.2.2 Control-flow integrity

Stateless CFI Defenses such as W

X policies efficiently prevent codeinjections attacks. Defenses like ASLR and canaries make code-reuse

attacks harder, but do not prevent them entirely. CFI directly addresses

code-reuse attacks by enforcing a policy based on a pre-computed controlflow graph (CFG) for the protected program [2, 3]. Instrumentation then

checks that the forward-edges, e.g., indirect function calls, target a destination containing an expected identifier. The identifier is based on an

equivalence class (EC) derived from the CFG, such as that functions that

share call-sites belong to the same EC. This can result in an overly permissive policy [3]. Another approach is to route all indirect function calls via

jump-tables [153]. This allows the implementation of more restrictive policies. Nonetheless, carefully constructed code-reuse attacks can circumvent

stateless CFI solutions [137, 51, 72, 40].

**Fully-precise CFI** Fully-precise CFI is an idealized stateless CFI policy. It only allows control-flows that happen in some benign execution of a program. Unfortunately, if the benign execution allows multiple functions at a call-site, then even a fully-precise CFI must allow those targets.  $\mathscr A$  can thus still alter control-flow among those possible targets. Subsequently, even fully-precise CFI has been shown vulnerable to *control-flow bending* attacks [29].

**Shadow call stacks** Backward-edges in the CFG—for instance, a function return—can be enforced using a *shadow call stack* [25]. The shadow call stack is used to hold a secure copy of return addresses, and thus allows precise verification of returns. The shadow call stack must be protected for it to guarantee protection. It can be protected using software fault isolation [2]. Software-based shadow call stacks can be faster by placing them in the same address space and addressing them via a dedicated register [48, 25]. However, such approaches can leave the shadow call stack open to attack.

**Context-sensitive CFI** Shadow stacks are stateful, i.e., they do not follow a fixed statically determined CFG. However, they only protect function returns. Recent work has proposed solutions that combine static analysis and run-time tracking to implement stateful CFI policies. Such approaches restrict control-flows with respect to the whole execution path of the program [56, 111, 68]. The program execution flow is tracked using the

Intel Processor Trace (PT) [83, Vol.3C, Chap.35] and monitored from a separate monitoring process. This approach has been demonstrated to allow enforcement of unique control-flow targets [78]. Unfortunately, this does not come for free; the performance overhead of instrumentation is less than 5%, but the monitoring process incurs an additional overhead of about 10% [78].

Protecting code-pointers Control-flow attacks generally depend on manipulating code pointers (including the return address). A natural alternative to CFI is thus to focus on the protection of code pointers. *Code-pointer integrity* takes this approach [101]. It uses static analysis to identify and protect pointers by placing them in protected memory, called the *safe stack* [102]. An alternative to isolating pointers, is to cryptographically protect them. Cryptographic CFI (CCFI) uses message authentication codes (MACs) to verify the integrity of pointers before they are used [113]. The MAC is derived from the pointer's address and its type. Using a type-based MAC permits efficient instrumentation without the need for extensive static analysis. Approaches that protect code pointers provide exact CFI verification.

Clang CFI CFI implementations have been demonstrated on both GCC and LLVM compilers [153]. The LLVM / Clang compiler provides a stateless CFI mechanism [37]. In contrast to traditional CFI approaches, Clang uses type-based checking at call sites. In effect, it checks that indirect function calls are performed using pointers of the correct dynamic-type. In addition, Clang supports software-based shadow call stacks on 64-bit ARM architectures [38].

**Data-only attacks** Performance and compatibility questions aside, current defenses proposed in the literature offer comprehensive protection against code-reuse attacks. However, non-control data attacks do not alter any control-data, and therefore, do not violate CFI policies. Such attacks have been demonstrated to be possible on real-world applications [33]. Moreover, recent data-oriented programming (DOP) attacks show that non-control attacks can be used to perform arbitrary computations [79]. DOP is similar to ROP, but it does not directly alter control-flows to execute gadgets. Instead,  $\mathscr A$  alters data that affects control-flow decisions—e.g., loop iterations—to chain and select gadgets.

### 2.3 Memory safety

The attacks described in Section 2.2 are a result of memory errors and would all be prevented by guaranteed *memory safety*. Despite such widespread concern, the definition of memory errors remains elusive. There are efforts to formalize the notion of memory safety. This is valuable because it would

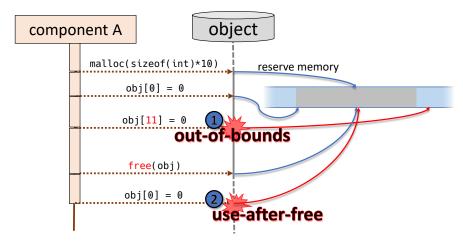

**Figure 2.3.** Memory errors can be either temporal (e.g., an out-of-bounds write  $\mathbf{0}$ ) or spatial (e.g., use-after-free error  $\mathbf{0}$ ).

allow the memory safety of a specific program to be verified. Unfortunately, the memory safety of a C program has been shown to be undecidable in the general case [136]. Other models have shown undecidability under multi-threading [169]. Nonetheless, recent work has moved towards more practical definitions that could possibly be applied to subsets of C / C++[14].

In practice, memory safety is often defined as the absence of *memory errors*. A memory error can be loosely defined as an error that causes unintended changes to memory. In the literature, the memory-error definition often depends on the research goals [77]. A common definition of memory safety is the absence of specific memory errors. For instance, Younan et al. [168] lists the following memory errors: 1) stack-based buffer overflows, 2) heap-based buffer overflows, 3) dangling pointer references, 4) format string vulnerabilities, and 5) integer errors. Even without an exact definition, it is intuitively clear that memory safety would prevent a large class of attacks.

### 2.3.1 Spatial and temporal memory safety

Szekeres, Payer, and Wei [151] categorize errors into *spatial* and *temporal* errors. When a memory read or write accesses memory out of bounds, a spatial memory error occurs. For instance, if an array is accessed with an index beyond its allocated size. A temporal memory error occurs when data is accessed after its allocated memory has been freed. For instance, *use-after-free* errors that occur when a variable is used after its allocated memory has been freed for other use. Although this separation does not provide a formal model, it highlights differences in both attacks and defenses. Figure 2.3 illustrates the difference between temporal and spatial memory errors.

**Spatial memory safety** Spatial memory safety is conceptually clear: a memory read or write should not touch *unintended memory*. In statically-typed and type-checked languages, unintended memory is often unambiguously specified by the type. The type then allows easy compile-time verification and run-time checking of memory accesses. C / C++ are statically-typed but allow casting to and from raw pointers. Raw pointers do not carry type (or size) information, and so do not support run-time type checking. A spatial memory error can corrupt the memory of unrelated data. As seen in Section 2.2, such errors can be used to implement expressive attacks.

### 2.3.2 Temporal memory safety

Temporal memory safety is, again, conceptually simple: a variable should not be used after its memory is deallocated. Some languages employ techniques such as garbage collection to deallocate memory automatically. Rust uses the concept of variable *ownership* and automatically deallocates memory when an owned variable goes out of scope [114]. In the context of C / C++, memory can be manually allocated and deallocated. A program must exercise care to deallocate an object only when it is no longer used. The use of shared objects can be tracked using *reference counters* in order to ensure safe deallocation [39]. When an object is prematurely deallocated and used afterward, a *use-after-free* error occurs. Because the memory might already have been assigned to other data, such errors are exploitable [168].

### 2.3.3 Memory safety in C/C++

There are many proposals for reaching memory safety in the C language. These can be roughly split into source-compatible approaches that do not require source code changes, and those that do. The latter consists of approaches such as Cyclone [86] and CCured [122], with CCured having a reported overhead of 25–214% in SPECINT 95 [122]. Checked-C takes the middle-ground by providing new checked pointers that can be used to convert C codebases gradually [60]. Nonetheless, even partial conversion incurs relatively high-overhead, with a reported average of 8.6%.

Source-compatible approaches use existing source code semantics and static analysis to implement memory safety checks. One approach for spatial memory safety is to protect allocation bounds, e.g., Purity [75] and AddressSanitizer [139]. These approaches use a shadow memory to define memory red zones that can be used to detect spatial and temporal memory errors. But they still incur a high overhead: AddressSanitizer has a reported slowdown of 73% [139]. AddressSanitizer is currently widely used in testing [11] and supported in the mainline Clang compiler [34]. However, allocation-based checking cannot detect inter-object overflows and has been shown vulnerable to attacks [69].

Another approach is to tie bounds to the pointer. Pointer-based bounds have the advantage that they can be *narrowed*. Narrowing can be used to limit a pointer to sub-structure within an object, instead of the allocation that encompasses the whole object. Pointer-based bounds can be realized with so-called *fat pointers*, i.e., a modifier pointer representation that includes its bounds [89]. Fat pointers are convenient, but cause compatibility errors due to the changed pointer representation. An alternative is to use disjoint metadata to track pointer bounds [127, 164, 54]. Baggy bounds checking is one such approach and incurs an overhead of 72% on SEPECINT 2000 [5]. SoftBound uses a similar approach but supports write-only checking to achieve an average overhead of only 15% [121].

### 2.4 Hardware-assisted memory safety

Due to the high overhead of most run-time protection schemes, there is a vested interest in providing hardware support. This includes hardware-assisted CFI (e.g., HAFIX [50] and CFI CaRE [124]) and run-time scope enforcement [50]. CHERI is a MIPS-based architecture that provides memory safety by using capability-based memory addressing [162]. CHERI capabilities have been shown to support Unix-like kernels and full software stacks [52]. Such research is valuable, but faces deployment challenges due to the need for hardware changes. However, hardware manufacturers have recently started rolling out new memory-safety primitives in their processors.

**Intel** Intel Memory Protection Extensions (MPX) is a hardware-assisted spatial memory safety feature introduced in the Skylake CPUs [125]. It supports pointer-based bounds checking similar to SoftBound [121] by providing new instructions for accessing bound metadata and checking bounds. Intel MPX is further explored in Publication I (Chapter 3). Intel Memory Protection Keys for Userspace (PKU) is an extension that can enforce that a protected memory region is accessed only when the process has enabled a specific key. In practice, the process itself tags memory regions for use with a specific key, and then loads that key into a configuration register. ERIM uses PKU to implement in-process isolation for userspace programs [155]. An upcoming feature in Intel processors is Control-flow Enforcement Technology (CET) [82]. It includes two components, a hardware-assisted shadow stack—similar to the software shadow call stacks discussed in Section 2.2.2—and indirect branch tracking. Indirect branch tracking enforces that the execution of a call or jump instruction is always followed by the execution of a special instruction that marks a valid target.

#### Background

ARM Pointer Authentication (PA) is a new feature introduced in the ARMv8.3-A architecture [8]. It provides cryptographic primitives to sign and verify pointers. It is used in Publications III–V and is further discussed in Chapter 5. New features in the later ARMv8.5-A architecture include branch target indicator (BTI) and Memory Tagging Extension (MTE) [8]. BTI is similar to the indirect branch tracking in Intel CET, although it allows separation of indirect function calls and indirect branches. MTE is somewhat similar to Intel PKU, but ties access permissions to pointers, not the process. A hardware-assisted variant of the AddressSanitizer has been demonstrated using MTE [140].

## 3. Linux kernel memory safety

The OS kernel is a security-critical piece of software that controls userspace applications. The Linux kernel is a unikernel, i.e., a monolithic kernel that controls everything from process scheduling to storage devices and networking. From an attacker's perspective, it is a lucrative target. Unfortunately, the Linux kernel is also written in C, which readily lends itself to memory errors (Section 2.2). Protecting the kernel is thus important. It is tempting to consider the application of userspace memory-protection schemes to the Linux kernel. But this poses three challenges:

- **C1** The kernel uses programming patterns that are incompatible with many established userspace defenses.

- **C2** The adversary model is different, i.e., the attacker 𝒜 operates outside the kernel.

- **C3** Many security mechanisms depend on kernel facilities or use it to provide integrity and confidentiality guarantees.

- C1 Incompatibilities depend on the security policy and its implementation. For instance, pointer-based memory safety could benefit from narrowing (Section 2.3.3). But the kernel implements inheritance using a model that is incompatible with narrowing. A subclass in the kernel is defined by placing the base class as a substructure at the end of the inheriting structure. If a pointer to the base class were narrowed, it could no longer access the inheriting class. Conflicts between the security policy and kernel programming patterns can be solved either by weakening the security policy or by modifying existing coding patterns.

- **C2** In users-space adversary models for memory safety,  $\mathscr{A}$  typically attacks a process from within it.  $\mathscr{A}$  aims to alter the behavior of the same process they interact with (Section 2.2). The kernel has a fundamentally different adversary model. It is attacked from outside and cannot be trivially reset. In userspace, it is relatively cheap to reset a misbehaving process without affecting the system as a whole. This allows defenses that

kill the process outright. This is not the case for the kernel; resetting the kernel affects all running applications and could in itself be considered a DOS attack. In the kernel adversary model,  $\mathscr A$  can typically launch arbitrary userspace programs, which then interact with the kernel, e.g., through system calls. The kernel can terminate an offending process, but this neither resets kernel defenses nor prohibits  $\mathscr A$  from retrying with a new process. This is particularly problematic for security mechanisms that rely on probabilistic defenses, e.g., kernel address space layout randomization (KASLR) [42].

C3 Userspace defenses often rely on services by a higher privilege level, e.g., the kernel. In the case of Intel MPX, the mechanism relies on the kernel to dynamically manage memory mappings in order to improve performance. But the dependency could also affect security, for instance, if the kernel is used to protect sensitive data. While the kernel could rely on the hypervisor, this might cause unreasonable performance overhead and complicate the implementation of such defenses.

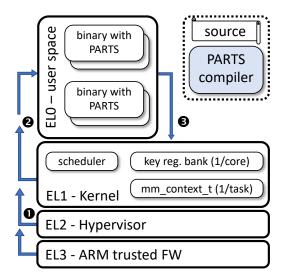

Practical kernel protection must consider both the specific run-time environment and the different adversary model. But the monolithic code base of the Linux kernel also has some advantages. It follows strict guidelines and coding practices, which lends itself to systematic protections. The kernel also uses its own Makefile-based build system kbuild [28], which allows clean integration of security features. Linux has also introduced kbuild support for GCC-plugins [44], and more recently added support for building the kernel with LLVM / Clang [105]. In Publication I, we leverage these aspects to address two classes of bugs within the Linux kernel: temporal memory errors caused by reference counter overflows, and spatial memory errors.

### 3.1 Background: Intel MPX and reference counters

### 3.1.1 Reference counters

As mentioned in Section 2.3.2, reference counters are a technique for the safe deallocation of objects [39]. A reference counter is conceptually simple: it is an integer that tracks the number of references to an object [39]. When the count reaches zero, this implies that the referenced object is no longer used and that its memory can be freed for other uses. An ideal reference counter provides only an initialization instruction, and conditional increment and decrement instructions. The exact value of the counter is not needed, and it is sufficient for the increment and decrement to return success on non-zero values.

Reference counter overflows Integer overflow is a memory error [168] that results in undefined behavior [85, 55]. On most contemporary processor architectures, an overflow will follow two's complement semantics, i.e., an integer with the value INT\_MAX will be set to INT\_MIN when incremented. Integers in Linux kernel always follow this behavior due to compiler configuration. A reference counter can thus overflow and incorrectly reach zero through repeated incrementing.

The number of references is typically bound by resource limitations. Hence, a reference counter remains small enough to avoid integer overflows. However, a program error could allow the counter to be incremented without allocating resources. This could allow  $\mathscr A$  to increment the counter indefinitely, thereby causing the counter to overflow. This will trigger object deallocation and subsequently cause a *use-after-free* error (Section 2.3.2). In the context of the Linux kernel, reference counter overflows have been shown to be exploitable.  $^2$

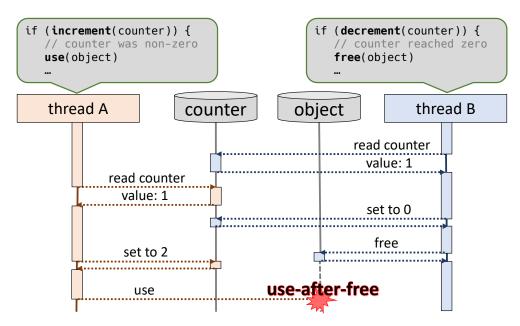

Concurrency and reference counters Reference counter semantics must remain sound when accessed concurrently. The counter must be atomically and conditionally modified on object acquisition and release. This prevents time-of-check-time-of-use (TOCTOU) type errors that could result in use-after-free errors (Figure 3.1). Modern CPUs support out-of-order execution that allows the CPU to reorder instructions on a micro-architectural level as long as the architectural result remains the same. For example, the CPU might reorder load instructions to improve the locality of memory loads. Memory barriers, i.e., instructions that guarantee partial or full ordering of memory reads and writes, can be used to prevent this.

Reference counters in the Linux kernel To avoid concurrency issues, the Linux kernel versions prior to v4.14 implemented reference counters using the atomic\_t type. It provides an atomic application programming interface (API) for an integer and guarantees partial memory ordering [115]. Memory ordering is guaranteed either using architecture-specific memory barriers, or a generic implementation based on spin-locks. The kernel also provides the kref type, which is designed for reference counting and implemented with atomic\_t [99, 115]. Unfortunately, kref is sparsely used, leading to a multitude of hand-crafted reference counter implementations based on atomic\_t.

Reference counters in the Linux kernel often serve multiple purposes. For instance, the sk\_wmem\_alloc reference counter also tracks the message transfer queue for the network layer. Hence, it needs to read the exact counter value and perform arbitrary additions or subtractions. To further

<sup>&</sup>lt;sup>1</sup>This behavior is guaranteed irrespective to CPU architecture by using the -fwrapv and -fno-strict-overflow compiler flags.

<sup>&</sup>lt;sup>2</sup>Reference counter errors were exploited, for instance, in CVE-2014-2851, CVE-2016-4558, CVE-2016-0728, CVE-2017-7487 and CVE-2017-8925.

**Figure 3.1.** Non-atomic reference counters could result in an object being freed by a thread **A** while concurrently being acquired by another thread **B**.

complicate matters, atomic\_t is not exclusive to reference counters. Due to such varied use, reference counters cannot be automatically identified and found without developer intervention.

#### 3.1.2 Intel MPX

The Intel Memory Protection Extensions (MPX) is a pointer-based spatial memory safety mechanism (Section 2.3.1). It debuted in the Skylake architecture [134, 125]. MPX provides new instructions for managing and checking pointer bounds; and new registers for configuring MPX and storing bounds. The pointer bounds are stored in separate metadata without changing the representation of pointers. The Intel ICC compiler supports MPX, and GCC added support in GCC 5.0 [125], although the latter has since version 9.1 dropped support [67]. Because MPX is pointer-based, it can perform *narrowing* (Section 2.3.3) and could potentially avoid vulnerabilities inherent to allocation-based bounds checking [69]. However, in practice, the GCC instrumentation must make concessions to avoid compatibility issues from strict narrowing [125].

MPX and temporal safety MPX is not designed to provide temporal memory safety, nor does it do so. The pointer used to free dynamically-allocated memory could be invalidated by setting its bounds to zero; however, there is no mechanism by which to invalidate other pointers to the same memory. Hence this would not prevent use-after-free errors. Oleksenko et al. [125] propose adding a lock-and-key mechanism that provides temporal safety using current MPX hardware.

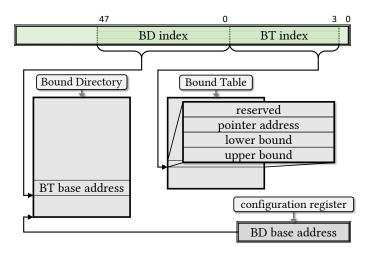

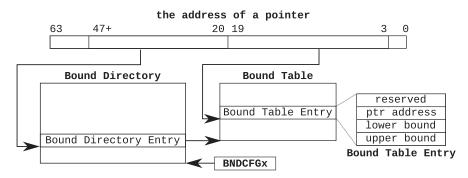

Figure 3.2. MPX bounds metadata uses a two-level mapping based on a pointer's address.

Pointer bounds data When accessing a pointer to stack-based data, the compiler can statically inject bounds information without the need for additional metadata. This is not always possible, e.g., when loading a pointer from shared global memory. For such cases, MPX provides the bndstx and bndldx instructions that store bounds in disjoint metadata. To check the bounds, they are first either loaded from the metadata or statically set by the instrumentation. The check is then done with the bndcl and bndcu instructions, which check the lower and upper bounds, respectively. Notably, a bounds check is performed in three distinct operations: 1) one to load or set the bounds into a bounds register, 2) one to check the lower bound, and 3) one to check the upper bound. This can cause TOCTOU type errors in multi-threaded applications because the pointer and its bounds are loaded as separate non-atomic actions.

Accessing pointer metadata The MPX bounds metadata is indexed based on the pointer's address using a two-level mapping, via a bound directory (BD) to a bound table (BT) that contains the bounds (Figure 3.2). The metadata must be managed by the software; the hardware instructions only accelerate the addressing and lookup. On GNU/Linux, the program reserves the address space for the BD and writes its address into a configuration register. On 64-bit systems, this is a 2GB memory range. Each 64-bit entry in the BD points to a 4MB BT, which in turn contains bounds for the pointers. The memory pages of the BD are mapped to physical memory only when written to. The individual BTs are similarly mapped ondemand; when bndldx / bndstx encounters an empty BT entry, they trigger a fault. The kernel manages the fault by mapping the 4MB memory space for the BT and then allows the userspace process to continue transparently.

#### 3.2 Results: refcount\_t and MPX in the Linux kernel

# 3.2.1 Preventing reference counter overflows in Linux

In Publication I, we present our work on protecting reference counters. We answer three questions: 1) how to properly handle reference counter overflows, 2) how to design an API for the Linux kernel, and 3) how to apply kernel-wide changes efficiently?

Handling of reference counter overflows Reference counter overflows must not be exploitable by causing the counter to reach zero while the referenced object is still in use. Performance requirements prevent heavy-handed approaches that maintain the value, e.g., by dynamically switching to a larger integer type [55]. But the vulnerability can be mitigated by *saturating* a reference counter on overflow [20]. A saturated counter is locked at its maximum value. Because the correct value is lost, the counter cannot be safely incremented or decremented after saturation. Instead, a saturated counter always returns success when incremented or decremented without changing its value. In effect, this converts an exploitable use-after-free error to a wasteful but otherwise harmless memory leak.

Design of refcount\_t We began our work by analyzing the design of the PAX\_REFCOUNT feature of the grsecurity Linux patches [20]. It first introduced the saturation mechanism by adding it directly to the atomic\_t type. PAX\_REFCOUNT also introduces a new atomic\_unchecked\_t type to support uses that depend on integer overflow. This unintuitively changes to atomic\_t behavior and requires changes in unrelated code that relied on the old behavior.

We initially explored the possibility of porting PAX\_REFCOUNT to the mainline kernel. However, after initial porting efforts, a new refcount\_t type was proposed by Peter Zijlstra [171]. It uses the saturation mechanism described above and also logs overflows to facilitate the fixing of the bugs that caused the overflow. Because refcount\_t is used for reference counting only, its semantics are self-documenting. Moreover, it incorporates compile-time checks that discourage unsafe use (e.g., ignoring return values of refcount\_t functions). Based on our porting efforts and analysis, we proposed API improvements that allowed for wider adoption by accommodating existing use cases.

Converting to refcount\_t To support future development and aid in our kernel-wide conversion efforts, we developed Coccinelle [152] patterns for reference counters. Coccinelle is a text matching and transformation tool that is used for automated patching and detection of problematic code. While it could not unambiguously distinguish reference counters from all other atomic\_t uses, it proved useful in detecting candidates for refcount\_t

conversion. Not only did we use our Coccinelle patterns to create over 200 accepted patches, but we also integrated the pattern with the kernel's Coccinelle code-quality checks.

#### 3.2.2 Using Intel MPX in the Linux kernel

MPX ostensibly supports kernel protection; for instance, by including configuration registers for ring-0 (i.e., kernel-space) execution. However, the metadata scheme cannot be trivially realized within the kernel. Not only because of the high overheads observed in userspace applications but more fundamentally due to the reliance on on-demand mapping. The kernel, as-is, cannot handle page-faults caused by itself. This means that the whole BD must be mapped to physical memory, or somehow always pre-emptively mapped before use. The BT allocation faces the same issue. Even an optimized approach that only reserves metadata for used kernel memory would increase memory use by 500% (e.g., for each possible 64-bit pointer a 64-bit BD-entry, and a 256-bit BT-entry).

Avoiding bounds metadata Our work in Publication I approaches this challenge by first realizing that the kernel already tracks its own memory allocations. We devised a way to utilize the kernel memory allocator to retrieve allocation-based bounds instead of using bndstx / bndldx. In practice, our instrumentation removes any bound metadata stores and replaces loads with a function that retrieves the allocation bounds from the allocator. This change removes additional memory requirements imposed by MPX. However, it also changes the pointer-based bounds checking to a mixed model that, in some cases, uses allocation-based bounds.

Implementation of MPXK Our prototype implementation, MPXK, builds on the prior GCC MPX instrumentation. MPXK adds new runtime functions to the kernel for loading allocation bounds. It then applies GCC MPX instrumentation. To apply our modifications, we used the new GCC compiler-plugin infrastructure and implemented our own MPXK plugin [44]. Our plugin replaces any metadata loads with calls to our added in-kernel functions.

#### 3.2.3 Discussion: tricky bugs and environments

Detection reference counter bugs Reference counter errors can be subtle and seldom cause directly observable side effects. In practice, even faulty reference counters are unlikely to overflow under benign conditions. The vulnerable code path would need to be exercised 2<sup>integer\_bit\_size</sup> times to trigger the overflow. Consequently, reference counter overflow can be oblivious to security-focused testing techniques such as fuzzing [16, 64]. However, a typical error is a missing counter decrement, which will inadvertently lead

to a memory leak that could be detected.

Security through better interfaces It could be argued that many errors are due to poor interfaces that lead to ad hoc solutions. Linux reference counters fit this description: they were traditionally implementing using hand-crafted implementations around atomic\_t. As the experience with PAX\_REFCOUNT exemplifies (Section 3.2.1), it is not always sufficient to provide better security. Changes must also be intuitive and self-documenting to be acceptable and support future use. However, as kref exemplifies (Section 3.1.1), clean and secure interfaces must also accommodate existing needs. The refcount\_t design takes the best of both: 1) it efficiently prevents overflows, 2) it has a clear use-case without surprising semantics, and 3) it provides a wide API but includes compiler warnings that promote safe use. This assessment is supported by the success of refcount\_t conversion efforts but also by its incompatibility with bugs. For instance, bugs caused by missing return value checks that lead to reference counter underflows.<sup>3</sup>

Mixed bounds checking As discussed in Section 2.3, memory safety is difficult to realize. MPXK takes a mixed approach to sidestep practical limitations, i.e., by using either static pointer-based bounds or dynamically loaded allocation-based bounds. However, allocation-based bounds checking has already been shown problematic [69]. It is likely that such results apply to the mixed approach of MPXK. Nonetheless, trade-offs and similar mixed approaches are often needed for deployable defenses. A useful avenue of research would be to explore how such real-world deployments can be systematically evaluated and compared.

MPX today As noted in Section 3.1.2, GCC has dropped MPX support since version 9.1 [67]. Nonetheless, several research projects utilize MPX in various ways but typically only use a subset of MPX instructions. For instance, SGXBounds [100] uses the bndcl and bndcu instructions to perform bounds checking within Intel SGX enclaves [45]. Due to the restricted address-space of an SGX enclave, SGXBounds can store the bounds within the unused bits of the pointer itself, thus not needing the MPX metadata. In other cases, MPX is used for more coarse-grained enforcement, which allows these approaches to forgo the metadata-use [96, 119, 132, 30].

Memory safety in restricted environments MPXK tackles the problem of bounds metadata within the Linux kernel. Some recent projects focus on protecting the kernel (e.g., kCFI [120] and KAISER [74]), but this space is still largely unexplored by the research community. In comparison to userspace, the kernel will introduce new requirements and restrictions for other defenses also. Such restrictions should be researched further. Moreover, other environments will impose different problems. Trusted

$<sup>^3</sup>$ lkml.org/lkml/2017/6/27/409

execution environments (TEEs)—which are discussed further in Chapter 4—are a good example; due to their explicit focus on safety-critical programs, their memory safety is of utmost concern. Defenses such as SGXBounds [100] indicate that this space also offers new challenges and opportunities for novel memory safety solutions.

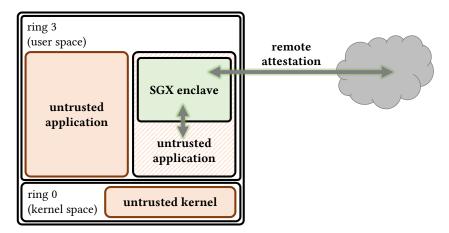

# 4. Intel SGX side-channels

Intel Software Guard Extensions (SGX) is a hardware feature introduced in the Intel Skylake CPUs [45]. It allows the creation of trusted execution environments (TEEs) called SGX enclaves. An enclave provides three main properties: 1) isolated execution, which prevents other processes from observing its execution state (e.g., CPU registers and enclave memory), 2) sealing, which binds sensitive data to a specific device, and 3) remote attestation, which a remote party can use to verify that specific software is running in an enclave on real SGX hardware. An enclave provides confidentiality and memory integrity within an untrusted environment, e.g., on an untrusted client device or on shared hosting (Figure 4.1).

An SGX enclave is set up by loading it from unprotected memory into enclave memory. The loaded memory, e.g., code and data, is *measured* to support integrity checks and attestation. To start the enclave, the processor is switched to enclave mode, and the execution transferred to a fixed enclave entry point. An enclave is a started from userspace and has the memory access permissions of the invoking process. It relies on the untrusted OS kernel for scheduling and other system services. However, SGX prevents the kernel and other execution modes from observing an enclave's execution state. It also ensures that data is encrypted when it leaves the CPU boundary and is written into memory.

Intel states that side-channels are not considered within the threat model of SGX [88]. However, SGX-enabled hosting services are currently offered by several companies (e.g., Microsoft Azure [117], IBM Data Shield [81]). Considering that SGX is used in such environments, side-channels are a concern irrespective of Intel's envisioned threat model.

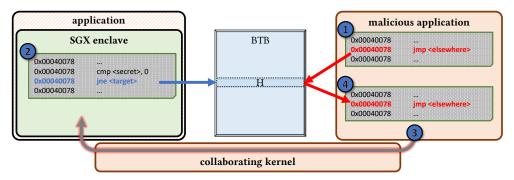

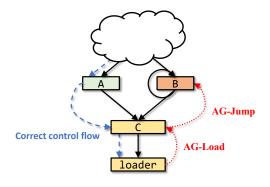

In Publication II we investigate a *branch-shadowing* side-channel on Intel SGX. Like other software side-channels—e.g., cache side-channels—it infers confidential data by observing changes in micro-architectural behavior caused by the processing of that data. Specifically, it exploits the behavior of branching instructions. This makes traditional defensive programming approaches ineffective [4]. Compile-time instrumentation can directly control branch instruction, and therefore, is ideal for addressing

**Figure 4.1.** An Intel SGX enclave is a TEE within an otherwise untrusted system. Remote attestation can be used to establish a trusted communication channel to a remote enclave.

this side-channel (RQ1).

# 4.1 Background: side-channels and SGX

A side-channel consists of some observable property that depends on a targeted confidential property. For example, the power consumption of a device could be used to leak secret keys from a device [95]. Side-channels can be divided into physical and software side-channels. The distinction can be fuzzy, as software interfaces can give access to physical properties. In this work, we focus solely on software side-channels. They are interesting because they do not require physical access and could be used remotely. An attacker  $\mathscr A$  on a virtual hosting platform could use software-only side-channels to attack co-located virtual machines (VMs).